# Thermal-Aware IC Chip Design by Combining High Thermal Conductivity Materials and GAA MOSFET

Young Suh Song

Department of Electrical and Computer Engineering

Seoul National University (SNU)

Seoul, Republic of Korea

e-mail: sys1413@snu.ac.kr

Shiromani Balmukund Rahi Department of Electrical Engineering Indian Institute of Technology (IIT) Kanpur Kanpur, India e-mail: sbrahi@gmail.com

Abhishek Kumar Upadhyay Institut Grundlagen der Elektrotechnik/Elektronik Technische Universität, Dresden Dresden, Germany e-mail: meetabhishek14@gmail.com

Abstract—The high integration of integrated circuit (IC) chip design has made thermal-aware design as one of the first priorities of the modern IC chip industry. Even though the modern IC chip technologies have aimed to achieve thermal stability by optimizing circuit design, the rapidly growing integration requires thermal-aware design not only in circuit level but also in transistor level. Such thermal-aware design with bottom-up (from the transistor level to the packaging level) can be used to reliable IC chips. Moreover, since aluminum oxide (Al<sub>2</sub>O<sub>3</sub>, also known as alumina) is compatible with CMOS fabrication process and has excellent thermal conductivity, it is possible to efficiently accomplish the improved thermal-aware design. Specifically, Al<sub>2</sub>O<sub>3</sub> has 59 times thermal conductivity compared to HfO<sub>2</sub>, and 19 times thermal conductivity compared to SiO2. In this paper, considering the outstanding thermal characteristics of Al<sub>2</sub>O<sub>3</sub>, we propose a comprehensive improvement including thermal characteristics by combining Al<sub>2</sub>O<sub>3</sub> and GAA MOSFET. As a result, the maximum lattice temperature  $(T_{max})$  in transistor has been significantly improved from 624 K to 518 K. In addition, capacitance of transistor could be also decreased, which will give benefits to inverter delay and three-stage ring oscillator (RO3) delay in IC chip.

Keywords—Integrated Circuit (IC) Design; Thermal-aware Design; Thermal Characteristics; Thermal Conductivity; Low-Power Design; Aluminum Oxide

#### I. INTRODUCTION

With increasing integration of the Integrated Circuits (IC), thermal-aware design emerges as one of the first priorities of Shubham Tayal

Department of Electrical and Computer Engineering

SR University

Warangal, India

e-mail: shubhamtayal999@gmail.com

Jang Hyun Kim

Department of Electrical Engineering

Pukyong National University

Busan, Republic of Korea

e-mail: janghyun@pknu.ac.kr

Byung-Gook Park

Department of Electrical and Computer Engineering

Seoul National University (SNU)

Seoul, Republic of Korea

e-mail: bgpark@snu.ac.kr

modern IC chip technology [1]. According to this demand, many researches have been broadly conducted for achieving thermal-efficient circuit design [2, 3]. However, even though this conventional approach with circuit optimization has successfully suppressed heat-generation, the novel IC chip made from sub-7 nm technology node requires more heat optimization [4-7]. Therefore, it has been widely accepted that IC chip needs to be thermally optimized not only in circuit level, but also in transistor level.

Unfortunately, most of transistor research has aimed to improve its own electrical characteristics, and the thermal characteristics has been not broadly researched [8-12]. This is because the improvement in thermal characteristics usually conflicts with improvement in electrical characteristics. For example, modern CMOS industry (such as *Intel*, *AMD*) plans to adopt gate-all-around (GAA) transistor structure for replacing FinFET structure and accomplishing low-power operation [13, 14]. However, since gate insulator (gate dielectric material) in GAA MOSFET completely wraps around silicon (Si) channel, the heat becomes hard to be dissipated.

This self-heating effect (SHE) not only degrades electrical characteristics, but also degrades several reliability issues in IC chip such as metallization lifetimes of circuit [15, 16], negative-bias temperature instability [17], hot-carrier induced degradation [18]. In this paper, for improving these concerns, novel GAA MOSFET structure is proposed by utilizing high thermal conductivity of  $Al_2O_3$ .

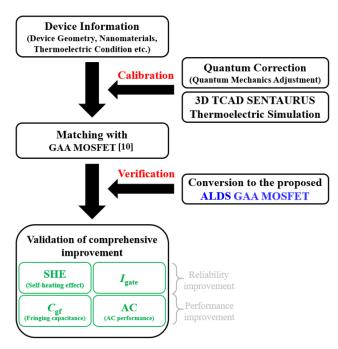

Figure 1. Overall workflow for validation of the proposed thermal-aware device design. From the proposed device structure, the thermal characteristics (SHE) and capacitance are simultaneously improved. Due to capacitance improvement, circuit performance such as RO3 delay, RC delay, inverter delay could be also improved.

### II. MAIN PURPOSE OF THE PROPOSED DESIGN METHODOLOGY

In our research, 2 main design goals are carefully adopted. First, for improving thermal performance of IC chips, thermal-aware design is adopted. Specifically, in designing transistor, the first goal is to suppress the increase of temperature during device operation.

Second, our research aims to improve the capacitance (C) of transistor. By doing so, our research tries to design low capacitance transistor for better circuit operation such as three-stage ring oscillator (RO3) delay, RC delay, and inverter delay.

#### III. WORKFLOW AND CALIBRATION PROCESS

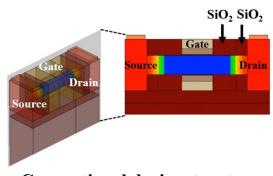

Fig. 1 illustrates the overall workflow of this research. In order to reliably simulate the proposed structure with GAA MOSFET, the calibration of GAA MOSFET is carefully conducted and then the proposed Al<sub>2</sub>O<sub>3</sub>-based dual spacer (ALDS) structure is incorporated. Finally, the validation of the proposed ALDS GAA MOSFET is performed in terms of thermal characteristics and electrical characteristics.

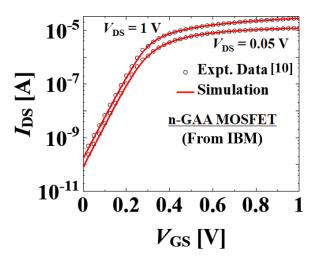

During calibration, quantum correlations are carefully performed for  $I_{DS}$ - $V_{GS}$  calibration under Synopsys Sentaurus<sup>TM</sup> 3D TCAD simulation tool [19]. Firstly, the electron mobility model (phumob/Enormal(Lombardi)/thin layer) is applied to consider interfacial surface calibration roughness scattering and Coulomb scattering. Then, quantum

Figure 2. Calibration results with basic transfer characteristics ( $I_{\rm DS}$ - $V_{\rm GS}$ ). This figure shows that our simulation data is well fit with the real measured data [10].

model and velocity saturation model are applied, and gate work function (WF) is carefully adjusted. Finally, the thermal conductivity of nanomaterials, heat conduction paths, and thermal boundary condition (300 K) to each heat dissipation path are carefully applied for analyzing thermal characteristics.

As a result, Fig. 2 demonstrates that our simulation results are well fit with the measured data of GAA MOSFET [10, 11].

#### IV. DEVICE STRUCTURE AND MODEL PHYSICS

#### A. Device Structure

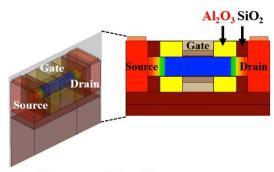

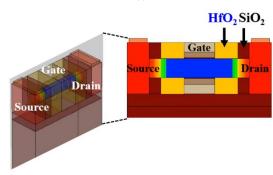

For a fair comparison, the proposed ALDS GAA MOSFET [Fig. 3(a)] is compared with the previous dual spacer (DS) GAA MOSFET (HfO<sub>2</sub>) [Fig. 3(b)] and the conventional GAA MOSFET (SiO<sub>2</sub>) [Fig. 3(c)]. In the previous DS GAA MOSFET [Fig. 3(b)], P. K. Pal *et al.* intelligently utilized high-κ material (HfO<sub>2</sub>) as inner spacer of DS, and SiO<sub>2</sub> as outer spacer of DS [12]. This previous DS structure was proposed for better inverter delay, and RO3 delay [12].

In designing all proposed structure, the 5-nm node technology values presented in the International Roadmap for Devices and Systems (IRDS) is carefully utilized  $(L_{\rm gate}/T_{\rm Si}/T_{\rm HfO2}/T_{\rm SiO2}=16/10/3/0.5~{\rm nm})$  [20].

In the proposed structure,  $Al_2O_3$  is incorporated as inner spacer (see Fig. 3(a)) to improve thermal characteristics. In addition, the proposed ALDS GAA MOSFET structure is also designed to improve electrical characteristics as well. The lower permittivity of  $Al_2O_3$  (compared to  $HfO_2$ ) improves alternating current (AC) performance and fringing capacitance ( $C_{gf}$ ), which will enhance circuit performance as well. In essence, our design methodology utilizes the high thermal conductivity and low permittivity of  $Al_2O_3$ .

## **Proposed device structure**(a)

### Previous device structure

### **Conventional device structure**

Figure 3. Schematic diagram of (a) the proposed device structure, (b) previous device structure, (c) conventional device structure. The proposed ALDS GAA MOSFET features dual spacer incorporating Al<sub>2</sub>O<sub>3</sub> for thermal improvement and AC performance improvement.

### B. Model Physics for Investigating Thermal and Electrical Characteristics

To investigate the thermal and electrical characteristics, several quantum mechanics model such as Shockley-Read-Hall (SRH) recombination, high field saturation, Fermi, and thermodynamic models are applied. In addition, Fowler Nordheim (FN) tunneling, trap-assisted-tunneling (TAT), and direct tunneling models are also considered for carefully investigating the electrical characteristics.

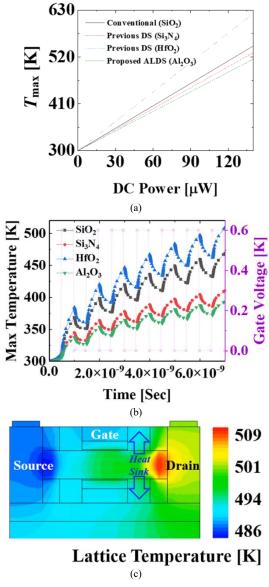

Figure 4. (a) Maximum temperature comparison with respect to DC power, (b) AC performance comparison with four different materials, (c) Cross-sectional view describing the location of heat sink and lattice temperature. Since the Al<sub>2</sub>O<sub>3</sub> in the proposed structure acts as effective heat sink, maximum temperature could be significantly improved.

#### V. SIMULATION RESULTS AND DISCUSSION

### A. Improvement of Thermal Performance by the Proposed ALDS GAA MOSFET

Fig. 4 explains thermal characteristics in four different structures. Regarding maximum temperature ( $T_{\rm max}$ ), the proposed ALDS GAA MOSFET shows best SHE due to the excellent thermal conductivity of Al<sub>2</sub>O<sub>3</sub> [Fig. 4(a)]. This thermal improvement also found in AC operation [Fig. 4(b)], since Al<sub>2</sub>O<sub>3</sub> in the proposed ALDS GAA MOSFET acts as effective heat sink [Fig. 4(c)].

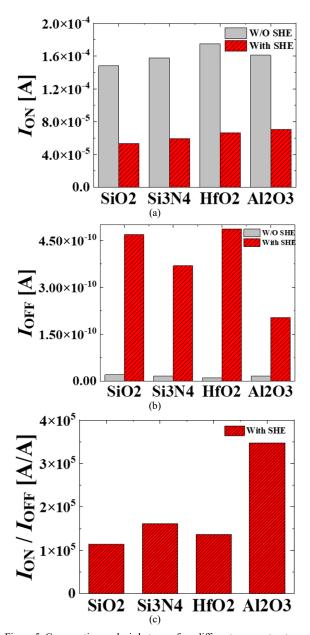

Figure 5. Comparative analysis between four different spacer structures under ideal condition (W/O SHE) and real condition (With SHE), in terms of (a) on-current ( $V_{\rm GS} = V_{\rm DS} = 0.6$  V), (b) off-current ( $V_{\rm GS} = 0$  V,  $V_{\rm DS} = 0.6$  V), and (c) on-off current ratio. Since the proposed structure has lowest increase of temperature during operation, it has highest electron mobility and highest on-current.

#### B. Improvement of On-current and Off-current by the Proposed ALDS GAA MOSFET

Fig. 5 illustrates the on-current ( $I_{on}$ ) comparison under ideal condition (W/O SHE) and real condition (with SHE). Under ideal condition (W/O SHE), the previous DS GAA MOSFET (HfO<sub>2</sub>) shows the best  $I_{on}$ , since HfO<sub>2</sub> has the highest permittivity (permittivity of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> =  $3.9\epsilon_0/7.5\epsilon_0/22\epsilon_0/8.9\epsilon_0$ ). However, under real condition (with SHE), our proposed ALDS GAA MOSFET shows best

$I_{on}$ , and then the previous DS GAA MOSFET (HfO<sub>2</sub>) follows [Fig. 5(a)]. This can be explained by the degradation of electron mobility due to temperature increase. Specifically, the previous DS GAA MOSFET (HfO<sub>2</sub>) has worst  $T_{max}$  due to the lowest thermal conductivity of HfO<sub>2</sub> [Fig. 4], and mobility degradation from SHE causes significant decrease of  $I_{on}$  in the previous DS GAA MOSFET (HfO<sub>2</sub>) [Fig. 5(a)]. On the other hand, the conventional GAA MOSFET (SiO<sub>2</sub>) shows the worst  $I_{on}$  performance, which means it is hard to be adopted to the next generation IC chips.

Regarding off-current ( $I_{\rm off}$ ), the previous DS GAA MOSFET (HfO<sub>2</sub>) shows highest  $I_{\rm off}$  [Fig. 5(b)], since the SHE causes the increase of  $I_{\rm off}$  due to increased energy of free electrons. As a result, the proposed ALDS GAA MOSFET shows best on-off current ratio ( $I_{\rm on}/I_{\rm off}$ ) [Fig. 5(c)].

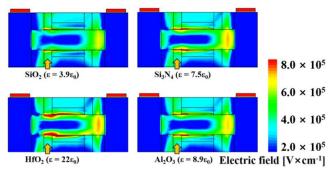

### C. Improvement of Capacitance by the Proposed ALDS GAA MOSFET

In addition, as illustrated in Fig. 6, the proposed ALDS GAA MOSFET also has better fringing capacitance ( $C_{\rm gf}$ ), compared to the previous DS GAA MOSFET (HfO<sub>2</sub>). This is because the Al<sub>2</sub>O<sub>3</sub> has permittivity of 8.9 $\epsilon$ <sub>0</sub>, which is smaller than the permittivity of HfO<sub>2</sub> (22 $\epsilon$ <sub>0</sub>). Therefore, when the proposed ALDS GAA MOSFET is adopted, the circuit performance (such as RO3 delay, RC delay, inverter delay) is also possible to be improved.

Figure 6. Distribution of electric field for comparing the fringing capacitance. Since  $Al_2O_3$  has lower permittivity compared to  $HfO_2$ , the proposed structure has better  $C_{\rm gf}$  compared to the previous structure with  $HfO_2$ . Therefore, our structure is expected to show better RO3 delay, RC delay, and inverter delay.

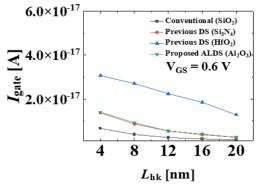

Figure 7. Gate current improvement achieved by the proposed structure ( $L_{\rm hk}$  stands for length of inner spacer). Compared to the previous DS structure (HfO<sub>2</sub>), our device structure shows better gate current characteristics.

#### D. Improvement of Gate Current by the Proposed ALDS GAA MOSFET

If gate current ( $I_{\rm gate}$ ) increases, the transistor's reliability becomes worse. This is because the gate current through gate insulator (gate dielectric oxide) deteriorates insulator quality and insulator will no longer properly act as insulator. This leads to fast failure in IC chips. Therefore, it is desirable to suppress  $I_{\rm gate}$  as much as possible.

As demonstrated in Fig. 7, the proposed ALDS GAA MOSFET also has better  $I_{\rm gate}$  characteristic, compared to the previous DS GAA MOSFET (HfO<sub>2</sub>). This is because the Al<sub>2</sub>O<sub>3</sub> has bandgap of 7.0 eV, which is greater than bandgap of HfO<sub>2</sub> (5.8 eV). Therefore, undesirable  $I_{\rm gate}$ , which degrades reliability of transistor and circuit, could be also suppressed by the proposed ALDS GAA MOSFET.

Namely, comprehensive improvement of four characteristics ( $T_{\rm max}$ , AC performance,  $C_{\rm gf}$ ,  $I_{\rm gate}$ ) could be achieved by the proposed ALDS GAA MOSFET. In essence, our proposed structure utilizes the advantage of high thermal conductivity, low permittivity, high bandgap of Al<sub>2</sub>O<sub>3</sub>.

#### E. Plans for Future Research

This paper has demonstrated electrical/thermal performances improvement, especially in transistor level. According to the result shown in this research, it is quite expected that our proposed design technique will be also possible to improve circuit performance. In accordance with this expectation, our research group is going to expand our field of research on circuit level. Especially, we are going to research improvement of gain in CMOS amplifier achieved by the improvement of transistor performance. In addition, more in-depth research will be also conducted to specifically investigate the effect of spacer length  $(L_{HfO2})$  on transistor performance and circuit performance. Our research group would like to show appreciation to the reviewers of 2022 International Conference on Circuits, Systems and Simulation (ICCSS) for their times and efforts to generously review this manuscript. In addition, the authors are deeply appreciated in advance the times and efforts that the anonymous referee of IEEE Transactions on Electron Devices (IEEE TED) will generously share for reviewing our future research.

#### VI. CONCLUSION

In order to effectively perform thermal-aware design in IC chips, we designed thermally efficient transistor. Due to the excellent thermal conductivity of aluminum oxide ( $Al_2O_3$ , alumina), the maximum temperature ( $T_{max}$ ) has been significantly decreased from 624 K to 518 K. In addition, our transistor also has additional advantages in terms of capacitance (C), which will enable improvement in three-stage ring oscillator (RO3) delay and inverter delay in upcoming IC chips. In essential, our proposed structure utilizes the high thermal conductivity, low permittivity, and high bandgap of  $Al_2O_3$ . Our proposed structure is very strategic for the future scaling IC chip technology with improved device reliability.

#### ACKNOWLEDGMENT

This work was supported by the 2022 research fund of Korea Military Academy (Hwarangdae Research Institute). Young Suh Song is also with Department of Computer Science, Korea Military Academy, Seoul 01805, Republic of Korea.

#### REFERENCES

- [1] A. Rezaei, Y. Shen, S. Kong, J. Gu and H. Zhou, "Cyclic locking and memristor-based obfuscation against CycSAT and inside foundry attacks," 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2018, pp. 85-90, doi: 10.23919/DATE.2018.8341984.

- [2] A. Jain, R. E. Jones, R. Chatterjee and S. Pozder, "Analytical and Numerical Modeling of the Thermal Performance of Three-Dimensional Integrated Circuits," in IEEE Transactions on Components and Packaging Technologies, vol. 33, no. 1, pp. 56-63, March 2010, doi: 10.1109/TCAPT.2009.2020916.

- [3] A. Jain, R. E. Jones, Ritwik Chatterjee, S. Pozder and Zhihong Huang, "Thermal modeling and design of 3D integrated circuits," 2008 11th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, 2008, pp. 1139-1145, doi: 10.1109/ITHERM.2008.4544389.

- [4] Z. Chen, J. Liu, J. Zhen and L. Sun, "Investigation of the Dynamic Thermal Characteristic in Bulk FinFET," 2018 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2018, pp. 251-253, doi: 10.1109/SISPAD.2018.8551664.

- [5] S. J. Kang, J. H. Kim, Y. S. Song, S. Go and S. Kim, "Investigation of Self-Heating Effects in Vertically Stacked GAA MOSFET With Wrap-Around Contact," in IEEE Transactions on Electron Devices, doi: 10.1109/TED.2022.3140283.

- [6] Y. S. Song, S. Kim, G. Kim, H. Kim, J.-H. Lee, J. H. Kim, and B.-G. Park, "Improvement of self-heating effect in Ge vertically stacked GAA nanowire pMOSFET by utilizing Al2O3 for high-performance logic device and electrical/thermal co-design," Japanese Journal of Applied Physics, vol. 60, pp. SCCE04, March 2021, doi: 10.35848/1347-4065/abec5c.

- [7] Y. S. Song, H. Kim, J. Yu, J. Lee, "Improvement in Self-Heating Characteristic by Utilizing Sapphire Substrate in Omega-Gate-Shaped Nanowire Field Effect Transistor for Wearable, Military, and Aerospace Application," Journal of Nanoscience and Nanotechnology, vol. 21, no. 5, pp. 3092-3098, May 2021, doi: 10.1166/jnn.2021.19149.

- [8] Jae Young Song, Woo Young Choi, Ju Hee Park, Jong Duk Lee and Byung-Gook Park, "Design optimization of gate-all-around (GAA) MOSFETs," in IEEE Transactions on Nanotechnology, vol. 5, no. 3, pp. 186-191, May 2006, doi: 10.1109/TNANO.2006.869952.

- [9] M. Kumar, R. S. Gupta, S. Haldar and M. Gupta, "A comparative assessment of Schottky-Barrier Source/Drain GAA MOSFET with conventional and junctionless GAA MOSFETs," 2013 Annual IEEE India Conference (INDICON), 2013, pp. 1-6, doi: 10.1109/INDCON.2013.6726127.

- [10] S. Bangsaruntip et al., "High performance and highly uniform gateall-around silicon nanowire MOSFETs with wire size dependent scaling," 2009 IEEE International Electron Devices Meeting (IEDM), 2009, pp. 1-4, doi: 10.1109/IEDM.2009.5424364.

- [11] Y. S. Song, J. H. Kim, G. Kim, H. -M. Kim, S. Kim and B. -G. Park, "Improvement in Self-Heating Characteristic by Incorporating Hetero-Gate-Dielectric in Gate-All-Around MOSFETs," in IEEE Journal of the Electron Devices Society, vol. 9, pp. 36-41, 2021, doi: 10.1109/IEDS.2020.3038391.

- [12] P. K. Pal, B. K. Kaushik and S. Dasgupta, "Investigation of Symmetric Dual-k Spacer Trigate FinFETs From Delay Perspective," in IEEE Transactions on Electron Devices, vol. 61, no. 11, pp. 3579-3585, Nov. 2014, doi: 10.1109/TED.2014.2351616.

- [13] X. Wang et al., "Design-Technology Co-Optimization of Standard Cell Libraries on Intel 10nm Process," 2018 IEEE International Electron Devices Meeting (IEDM), 2018, pp. 28.2.1-28.2.4, doi: 10.1109/IEDM.2018.8614662.

- [14] T. Singh et al., "2.1 Zen 2: The AMD 7nm Energy-Efficient High-Performance x86-64 Microprocessor Core," 2020 IEEE International Solid- State Circuits Conference - (ISSCC), 2020, pp. 42-44, doi: 10.1109/ISSCC19947.2020.9063113.

- [15] B. K. Liew, N. W. Cheung, and C. Hu, "Effects of self-heating on integrated circuit metallization lifetimes," in IEDM Tech. Dig., Dec. 1989, pp. 323–326.

- [16] M. Luthra, "Process challenges and solutions for embedding Chip-On-Board into mainstream SMT assembly," Proceedings of the 4th

- International Symposium on Electronic Materials and Packaging, 2002., 2002, pp. 426-433, doi: 10.1109/EMAP.2002.1188877.

- [17] D. K. Schroder and J. A. Babcock, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," J. Appl. Phys., vol. 94, no. 1, pp. 1–18, Jun. 2003.

- [18] N. Sano, M. Tomizawa, and A. Yoshii, "Temperature dependence of hot carrier effects in short-channel Si-MOSFETs," IEEE Trans. Electron Devices, vol. 42, no. 12, pp. 2211–2216, Dec. 1995.

- [19] Version K-2015.06-SP1, Synopsys Inc., Mountain View, CA, USA, 2017.

- [20] The International Technology Roadmap for Semiconductors (ITRS), 2017.