## Investigation of Analog Parameters and Miller Capacitance Affecting the Circuit Performance of Double Gate Tunnel Field Effect Transistors

Deepak Kumar, Shiromani Balmukund Rahi, and Piyush Kuchhal

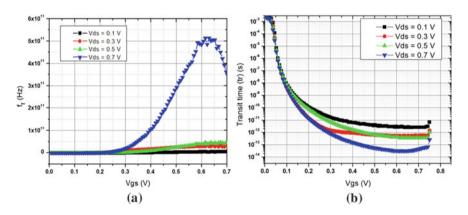

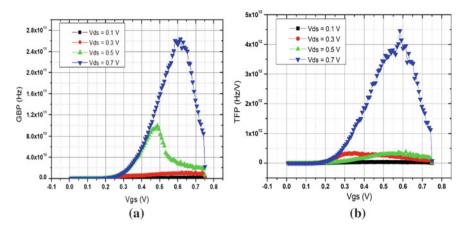

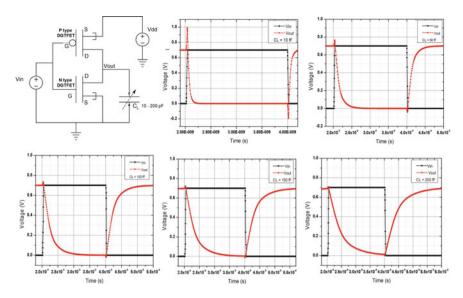

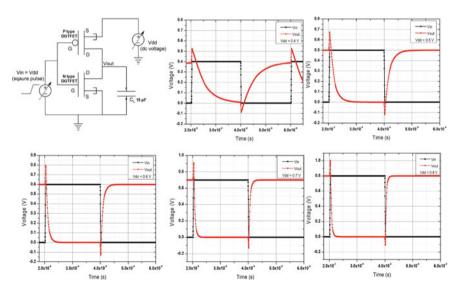

Abstract TCAD Simulations for 30 nm double gate tunnel field effect transistor (DGTFET) reports steeper subthreshold swing, SS ~ 15 mV/dec,  $I_{ON}$  ~  $10^{-4}$  A/ $\mu$ m, and low off-state current  $I_{OFF} \sim 10^{-15}$  A/ $\mu$ m as desirable parameters for low voltage applications. The unity gain frequency  $(f_T)$  increases with  $V_{gg}$  and maximizes at 5.2  $\times$  10<sup>11</sup> Hz for  $V_{\rm gs} = V_{\rm ds} = 0.7$  V. It is investigated that the gain-bandwidth product (GBP) also increase with Vgs and maximized at  $2.63 \times 10^{11}$  Hz for  $V_{\rm ds} = 0.7$  V at  $V_{\rm gs} = 0.6$  V. Transconductance frequency product (TFP) increases initially with  $V_{\rm gs}$  (0–0.7 V) and maximizes at 4.46  $\times$  10<sup>11</sup> Hz/V for  $V_{\rm ds}=0.7$  V. Higher value of  $V_{\rm ds}$  results in better response time of the DGTFETs, i.e., increasing  $V_{\rm ds}$  from 0.1 to 0.8 V, the transit time  $(t_r)$  of the electron decreases from 4 to 0.1 ps resulting faster switching operation. Transient performance of DGTFETs reports that at supply voltage  $(V_{\rm DD}) = 0.7$  V, increasing the load capacitance  $(C_{\rm L}, 10-200 \text{ pF})$  the total delay increases from 0.18 to 1.9 ns. It is also noticed that the \% peak voltage overshoot (%  $V_p$ ) decreases from 42.8 to 2.14% due to decrease in computed values of miller capacitance ( $C_{MIL}$ ) from 11.27 to 4.32 fF. Maintaining  $C_{L} = 15$  fF, increasing  $V_{DD}$ reports significant variation in voltage peak overshoot from 35 to 26.25% and total delay also decreases from 8 to 0.2 ns for  $V_{\rm DD} = 0.1 - 0.8 \text{ V}$ .

**Keywords** Band-to-band tunneling (BTBT) · Analog · Transient · TFET · Miller capacitance · Verilog A model · Symica D

D. Kumar (⋈)

Department of Electrical and Electronics Engineering, University of Petroleum and Energy Studies, Dehradun 248007, Uttarakhand, India

e-mail: d.kumar@ddn.upes.ac.in

S. B. Rahi

Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur 208016, India

e-mail: sbrahi@gmail.com

P. Kuchhal

Department of Applied Sciences, University of Petroleum and Energy Studies, 248007 Dehradun, India

e-mail: pkuchhal@ddn.upes.ac.in

© The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd. 2021 S. Choudhury et al. (eds.), *Intelligent Communication, Control and Devices*, Advances in Intelligent Systems and Computing 1341,

#### 1 Introduction

The transistor density is continuously increasing with scaling conventional— MOSFETs which results in huge power dissipation inside integrated chips (ICs). The aggressive scaling of supply voltage  $(V_{DD})$  for the CMOS devices which further reduces the dynamic power dissipation ( ${\sim}C_L \times V_{DD}^2$ ) and same is low-power applications for advance technology nodes [1–4]. The threshold voltage  $(V_{th})$  is needed to be scaled down proportionally as the supply voltage  $(V_{DD})$  along with dimensional scaling to achieve sufficient on current  $(I_{ON})$  in order to maintain satisfactory circuit and device performance. But Scaling down  $V_{\rm th}$  further increases off-state current  $(I_{\text{OFF}})$  significantly, hence increases static leakage power dissipation ( $\sim V_{\text{DD}} \times I_{\text{OFF}}$ ) irrespective of scaled down  $V_{\rm DD}$  and these impacts can be understood by the limitation of subthreshold swing (SS ~ 60 mV/decade) in MOSFETs due to conventional thermionic emission of electrons from source to channel. Therefore, it becomes essential to explore other structures of (FETs), those that have the potential to function at low supply voltage  $(V_{\rm DD})$ , hence minimize the switching power. To meet these expectations, a new semiconductor device architecture based on quantum transport mechanism (QTM), called Tunneling Field Effect Transistor (TFET) is studied nowadays [5–16]. TFETs can be considered as a potential device structure for ultralow power applications due to their band-to-band (B2B) tunneling transport phenomenon [17–25]. Furthermore, the TFETs possess high-k dielectric for deposition over the gate dimensions enhances the tunneling Electric field strength across junction formed across the body and the channel. Equation 1 shows that SS  $(\partial V_{GS}/\partial \log I_{DS})$  of the TFET consist of different parameter as compared to a MOSFET [26–30].

$$SS = \ln \ln(10) \left[ \frac{1}{V_{\text{eff}}} \frac{dV_{\text{eff}}}{dV_{\text{gs}}} + \frac{E+b}{E^2} \frac{dE}{dV_{\text{gs}}} \right]^{-1}$$

(1)

The Eq. 1 shows that SS is not limited by kT/q; can achieve a steep SS for lower gate voltages as compared to MOSFETs. The electric field (E) across the source-channel junction is another key parameter to reduce the SS (< SS  $\sim$  60 mV/dec) which further tends to reduce the subthreshold leakage power dissipation ( $E_{\rm L}$ ) in circuits as given by Eq. 2 [31, 32]. Due to its B2BT electron tunneling injection mechanism, a TFET has the potential to achieve lower SS particularly for low-power applications and have ability to cross the barrier of scaling limitations imposed by MOSFETs [30, 33–38].

$$E_{\rm L} \propto V_{\rm DD}^2 \cdot 10^{\frac{-\nu_{\rm DD}}{\rm SS}} \tag{2}$$

A 30 nm gate length double gate tunnel field effect transistor (DGFET) is simulated to achieve I-V and C-V characteristics in the Sentaurus 2D simulator. The features of the system are further used to evaluate the analog and transient (digital) output of DGTFETs by using Symica DE [39–45] to integrate a Verilog A model-based look-up table. The suitability of DGTFETs for analog applications is also studied by

comparing the analog output at different supply voltages  $(V_{\rm DD})$  of Double Gate (DG) n-channel TFETs. The analog parameters such as transconductance  $(g_{\rm m})$ , gain bandwidth product (GBP), transit time  $(t_{\rm r})$ , transconductance frequency product (TFP), and unity gain cut off frequency  $f_{\rm T}$  [46] are also reported as Si DGTFET performance.

In DG TFET, the source and drain region's charges are coupled due to B2BT process leads to significant increase in Cgd induces of miller capacitance at drain's node. The higher miller capacitance ( $C_{\rm MIL}$ ) may have an impact on the peak voltage overshoots during transient performance [47, 48]. In order to analyze the effect of  $V_{\rm DD}$  and load capacitance ( $C_{\rm L}$ ) on transient parameters and miller capacitance, digital simulations of DGTFETs based inverters are also reported.

## 2 Setup of Device Simulations for DGTFET

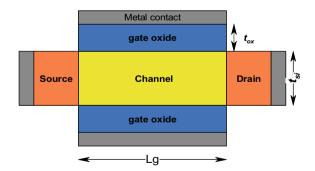

A DGTFET device structure is shown in Fig. 1 with the dimensions of the gate length  $L_{\rm g}=30$  nm, body thickness  $t_{\rm si}=7.0$  nm, gate oxide thickness  $t_{\rm ox}=1.0$  nm; body dielectric  $\varepsilon_{\rm si}=11.8\,\varepsilon_{\rm o}$ , oxide dielectric  $\varepsilon_{\rm ox}=21.0\,\varepsilon_{\rm o}$  (HfO<sub>2</sub>). For NTFET, the source is uniformly doped with Boron (B) of  $1.0\times10^{20}$  cm<sup>-3</sup>, doping of Phosphorus (P) of  $1.0\times10^{20}$  cm<sup>-3</sup> is done at the drain region and B of  $1.0\times10^{16}$  cm<sup>-3</sup> is doped in the channel region, respectively. Similarly for PTFET, the source is uniformly doped with P of  $1.0\times10^{20}$  cm<sup>-3</sup>, doping of B of  $1.0\times10^{20}$  cm<sup>-3</sup> is done at the drain region and B of  $1.0\times10^{16}$  cm<sup>-3</sup> is doped in the channel region, respectively. TCAD simulations are performed in order to carry out the electrical characteristic (I-V/C-V) by considering dc and ac signal at 5 MHz) analysis. Non local B2BT model, Fermi statistics, SRH recombination, Poisson's, and continuity equations are coded in the simulation script to achieve device simulation [49]. Simulations also considered gate metal work function and the width of the device of 4.2 eV and 1.0  $\mu$ m, respectively.

**Fig. 1** Structure of DGTFET used for TCAD simulation

#### 3 Results and Discussion

## 3.1 Analysis of I-V/C-V Characteristics of DGFET

Here in this structure, the intensity of electric field below the gate dielectric is enhanced by applying  $HfO_2$  as a gate dielectric which further results in enhancing the tunneling probability (Tp) of charge carriers as given by Eq. 3, and the same can be visualized from Fig. 2c; where  $\lambda$  is screen length,  $\Delta \phi$  is the tunneling barrier potential,  $E_g$  is energy band gap of silicon and m\* is the electron's effective mass [50].

$$T_{\rm p} \sim \exp\left[-\frac{4\lambda}{3} \cdot \frac{\sqrt{2m^*}}{h(\Delta\phi + E_{\rm g})} \cdot (E_{\rm g})^{1.5}\right]$$

(3)

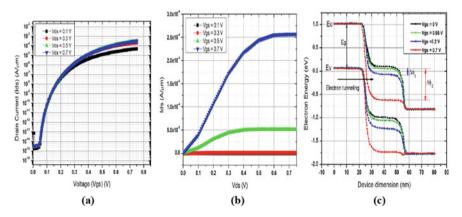

To understand the electrical characteristics of N type DGTFET, it is important to analyze its energy band diagram for the investigation of charge transport process. Figure 2a depicts the transfer characteristics ( $I_{\rm ds}-V_{\rm gs}$ ). The insignificant variations in I-V characteristics are noticed for  $V_{\rm ds}$  (0.1–0.7 V) at  $V_{\rm gs}$  (0.1 <  $V_{\rm gs}$  < 0.3 V). It is also observed that  $I_{\rm DS}$  increases with increasing  $V_{\rm ds}$  for higher values of  $V_{\rm gs}$ . For  $V_{\rm gs}$  = 0.3–0.7 V, a noticeable upward shift in the transfer characteristics is noticed for  $V_{\rm ds}$  between 0.1 and 0.3 V and after a further increase in  $V_{\rm ds}$  (>0.3 V), Ids shows saturation behavior. Figure 2a depicts that DG TFET possesses very low off current ( $I_{\rm OFF} \sim 5.0 \times 10^{-14}$  A/ $\mu$ m) which shows the capability to reduce power consumption ( $\sim V_{\rm DD} \times I_{\rm OFF}$ ) in standby mode for electronic circuits [51]. Simulation results indicate that this structure exhibits a steep subthreshold swing (SS  $\sim 15$  mV/dec), higher on-state current ( $I_{\rm ON} \sim 0.1$  mA/ $\mu$ m), and higher switching current ratio ( $I_{\rm ON}/I_{\rm OFF} \sim 5 \times 10^{10}$ ).

Fig. 2 a Transfer characteristics ( $I_{\rm ds}-V_{\rm gs}$ ) of DG NTFET, **b** Output characteristics ( $I_{\rm ds}-V_{\rm ds}$ ) of DG NTFET, **c** the energy band diagram of a simulated DG NTFET at  $V_{\rm ds}$  of 0.7 V showing tunnel barrier modulation

The current conduction phenomenon can be understood from the TCAD simulations of the energy band diagram as shown in Fig. 2c, which shows the off state ( $V_{\rm gs} = 0.0 \text{ V}$ ,  $I_{\rm ds} \sim 5 \times 10^{-14} \text{ A/}\mu\text{m}$ ) and the on-state ( $V_{\rm gs} = 0.2 \text{ V}$ ,  $I_{\rm ds} \sim 10^{-7} \text{ A/}\mu\text{m}$ ).

Output characteristics of NDGTFET are shown in Fig. 2b which shows the saturation point for  $I_{ds}$  at  $V_{ds} > 0.4$  V and for  $V_{ds} > 0.7$  V for  $V_{gs}$  0.5 and 0.7 V and higher output impedance can be also predicted for these  $V_{\rm ds}$  ranges. In the TFETs, the pinch is shifting to higher values of  $V_{\rm ds}$  for higher values of  $V_{\rm gs}$  as depicted in Fig. 2b. It is clearly seen that the conduction band of the channel region is not overlapping with the valence band of the source (P+) region (0.0 V <  $V_{gs}$  < 0.2 V) results in a wide tunneling barrier across the source-channel region as shown in Fig. 2c. In this situation, practical device current is very low and at this point, the device current is known as off-current ( $I_{OFF}$ ). A sharp energy band bending is noticed at the source–channel interface for  $V_{os}$  changes from 0.2 to 0.7 V, which further lowers the tunneling barrier across the source-channel interface, hence increases the Tp so that electrons get transported from the valence band of the source to the conduction band of the channel. The transportation of carriers takes place under the effect of B2BT. For a particular drain voltage, the higher the  $V_{\rm gs}$  (higher will be the electric field), the lower will be the tunneling barrier across the source-channel region and higher will be the electron tunneling probability resulting in higher tunneling drain current, Ids (see Eq. 3 and Fig. 2c).

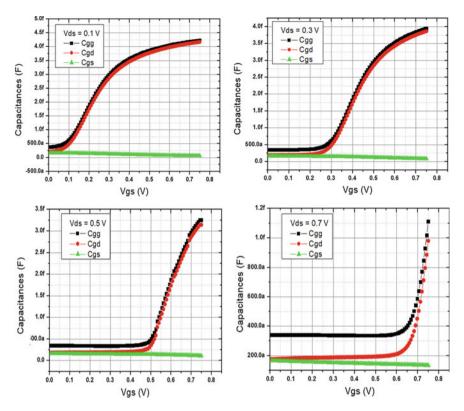

The C-V characteristics for NDGTFET show that the total gate capacitance ( $C_{\rm gg}$ ) is closely followed by drain capacitance ( $C_{\rm gd}$ ) for all the values of  $V_{\rm gs}$  as shown in Fig. 3 for  $V_{\rm ds}$  ranges, 0.1–0.7 V. This can be understood as charges of source-drain regions are directly coupled and governed by B2BT charge transport mechanism in Tunnel FET [23]. Source side tunnel barrier promotes the lower values of  $C_{\rm gs}$  (see Figs. 2c and 3) because there are insufficient minority carriers provided by the source, as the source junction is under reverse bias [52–54].  $C_{\rm gd}$  increases for  $V_{\rm gs}$  due to reduction in tunneling barrier. Increasing the  $V_{\rm ds}$ , a small amount of voltage drop occurs across drain to channel region resulting in lower values of  $C_{\rm gd}$  as compared to  $C_{\rm gs}$ . Higher the  $V_{\rm ds}$ , higher will be the voltage drop across the drain interface results lower values of  $C_{\rm gd}$  as clearly shown in Fig. 3. Higher drain voltage results in higher threshold voltage which further reduces energy barrier across the drain side (shifting of the conduction band of drain towards higher energy levels).

Further, the C-V curves are utilized to investigate and analyze the analog behavior of TFET and the same has reported, additionally, the transient simulations are carried out to analyze the impact of  $V_{\rm DD}$  and  $C_{\rm L}$  over the miller capacitance ( $C_{\rm MIL}$ ) in order to investigate the performance of DGTFET inverter.

## 3.2 Analysis of Analog Performance of DGTFET

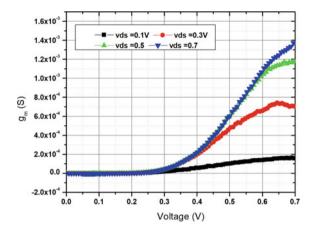

As for better amplification action, the FET device should be highly sensitive to the input signal variations and this feature of any amplifier is characterized by a small signal parameter called transconductance ( $g_{\rm m} = \partial I_{\rm DS}/\partial V_{\rm GS}$ ) which determines the

**Fig. 3** C-V Characteristics of TFET at various drain to source voltage  $(V_{ds})$

gain of the device required for designing of the analog amplifiers. The steep SS of DG TFET leads to higher values of  $g_{\rm m}$  are achieved. Figure 4 shows the  $g_{\rm m}$  for different values of  $V_{\rm ds}$  (0.1–0.7 V).

It is also seen from Table 1 that increasing the  $V_{ds}$  the ratio  $(r=g_{m2}/g_{m1})$  is also increases significantly from 2.33 to 7 for  $V_{ds}$  variations (0.1–0.7 V), respectively. From Fig. 4, it is observed that at the lowest value of  $V_{ds}=0.1$  V, the  $g_m$  is not showing the sensitive behavior for  $V_{gs}$ , i.e.,  $g_m$  increases only 2.33 times (from 0.75  $\times$   $10^{-4}(s)$  to  $1.75 \times 10^{-4}(s)$ ) for  $V_{gs}$  0.4 V to 0.7 V, respectively, as listed in Table 1. It can be seen from table  $g_m$  is more sensitive to  $V_{gs}$  for higher values of  $V_{ds}$  such that r=6 at  $V_{ds}=0.5$  V and r=7 at  $V_{ds}=0.7$  V, respectively, and this property is suitable for amplification action for FET devices in order to achieve the higher voltage gain.

Another critical parameter for amplification action is short circuit unity gain frequency  $(f_T)$  and transit time  $(t_r)$  which play a significant role in the analysis of frequency response and carrier transportation time, respectively. High frequency performance of analog circuits is explained in terms of unity gain frequency  $(f_T)$  as given by Eq. 4. Figure 5a shows the variation of cut off frequency  $(f_T)$  with  $V_{gs}$  of

Fig. 4 Impact of  $V_{ds}$  voltage on  $g_{m}$  for DGFET performance

Table 1 Listing the Impact of Vds on the g<sub>m</sub>

| V <sub>ds</sub> (V) | $g_{\rm m1}$ (S) at $V_{\rm gs} = 0.4$ V) | $g_{\rm m2}$ (S) at ( $Vgs = 0.7 \text{ V}$ ) | $r = g_{\rm m2}/g_{\rm m1}$ |

|---------------------|-------------------------------------------|-----------------------------------------------|-----------------------------|

| 0.1                 | $0.75 \times 10^{-4}$                     | $1.75 \times 10^{-4}$                         | 2.33                        |

| 0.3                 | $2 \times 10^{-4}$                        | $7 \times 10^{-4}$                            | 3.5                         |

| 0.5                 | $2 \times 10^{-4}$                        | $1.2 \times 10^{-3}$                          | 6                           |

| 0.7                 | $2 \times 10^{-4}$                        | $1.4 \times 10^{-3}$                          | 7                           |

Fig. 5 a Impact of drain to source voltage on cut off frequency  $(f_T)$  and **b** impact of drain to source voltage transit time  $(t_T)$

DGTFET device for various drain to source voltages.

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi \left(C_{\rm gs} + C_{\rm gd}\right)} \tag{4}$$

$$t_{\rm r} = \frac{1}{20 \cdot \pi \cdot f_{\rm T}} \tag{5}$$

As given in Eq. 4, the combined effect of different  $g_{\rm m}$  and capacitances ( $C_{\rm gs}$ ,  $C_{\rm gd}$ ) can be observed at cut off frequency ( $f_{\rm T}$ ). As seen from Fig. 5a, due to the higher gm value,  $f_{\rm T}$  initially increases with increasing  $V_{\rm GS}$  and reaches its peak value at  $0.1 \times 10^{11}$  Hz to  $5.2 \times 10^{11}$  Hz for  $V_{\rm ds} = 0.1$  V to 0.7 V, respectively. Afterward,  $C_{\rm gd}$  for rising  $V_{\rm gs}$  increases at a faster pace than gm. For low-power applications, the greater value of  $f_{\rm T}$  makes DG TFET attractive.

The frequency of unit gain  $(f_T)$  is also capable of investigating charge transport time in the FET and can be measured in terms of transit time  $(t_r)$ . The  $t_r$  is the time spent in transporting the carriers from the source to drain region and Eq. (5) has provided the same. Figure 5b demonstrates the transit time variance  $(t_r)$  with varying gate to source voltage  $(V_{gs})$  for the different drain to source voltage to investigate the effect of drain bias. As the inversion layer is substantially increased as the carriers now travel along a shorter path through the inversion layer and this effect can be clearly depicted from Fig. 5b showing  $t_r$  starts reducing with increasing  $V_{gg}$ . For a particular value of  $V_{\rm gs}$  (0 <  $V_{\rm gs}$  < 0.75 V), the lower values of transit time (4-0.1 ps) are noticed at the values of  $V_{\rm ds} = 0.1$ –0.7 V at  $V_{\rm gs} = 0.75$  V, respectively, as clearly depicted from Fig. 5b. Higher drain voltage results in a strong electric field in the vicinity of the drain and channel region which efficiently swept out the electrons from channel to drain. The t<sub>r</sub> also characterizes the switching ability of the FET devices and for fast switching operations, lower values of the transit time are preferred. Hence, it can be estimated as better switching ability of TFETs at higher drain voltages.

One of the major characteristics of the amplifiers for satisfactory operation is higher bandwidth. GBP is a parameter which shows how much the amplifier is capable to amplify the low frequency message signal and high frequency message signals. Figure 6a, b shows the impact of  $V_{\rm ds}$  versus  $V_{\rm gs}$  on GBP and TFP parameter, respectively, as given by Eq. 6 and 7.

$$GBP = \frac{g_{\rm m}}{20 \cdot C_{\rm ed}}; \tag{6}$$

$$TFP = \frac{g_{\rm m}}{Ids} * f_{\rm T} \tag{7}$$

It is another crucial investigation of DGFET performance for higher frequency application. From Fig. 6, it is clearly observed that GBP increases initially with Vgs because of increasing behavior of  $g_m$  and achieves maximum values of  $1.98 \times 10^9$  Hz,  $1.14 \times 10^{10}$  Hz,  $1 \times 10^{11}$  Hz, and  $2.63 \times 10^{11}$  Hz for different values of  $V_{\rm ds}$

Fig. 6 a Impact of  $V_{ds}$  on GBP; b impact of  $V_{ds}$  on TFP

= 0.1 V, 0.3 V, 0.5 V, and 0.7 V, respectively. TFP is also following the same trend such that it saturates at its maximum value of  $4.31 \times 10^{10}$  Hz/V,  $3.42 \times 10^{11}$  Hz/V,  $3.81 \times 10^{11}$  Hz/V, and  $4.46 \times 10^{12}$  Hz/V for different values of  $V_{\rm ds}$  for 0.1 V–0.7 V, respectively (see Fig. 6b). The driving point behind the GBP variations is the combined effect of  $g_{\rm m}$  and  $C_{\rm gd}$ , i.e., for a particular range of  $V_{\rm gs}$ ,  $g_{\rm m}$  is dominated by  $C_{\rm gd}$  and afterward  $C_{\rm gd}$  starts dominating over  $g_{\rm m}$  (see Figs. 2 and 4) resulting in peak values in GBP. It is observed that as  $V_{\rm ds}$  increases, the peaks of the GBP curves start shifting toward the higher values of  $V_{\rm gs}$ ; GBP peak at  $V_{\rm gs} = 0.49$  V for  $V_{\rm ds} = 0.5$  V and GBP peak  $V_{\rm gs} = 0.6$  V for  $V_{\rm ds} = 0.7$  V as depicted from Fig. 6a. TFP for  $V_{\rm ds} = 0.7$  V starts falling for  $V_{\rm gs} > 0.6$  V due to falling in f<sub>T</sub> (see Fig. 5a).

# 3.3 Transient Performance of TFET to Analyze the Impact on Miller Capacitance (C<sub>MIL</sub>)

In this section, the impact of supply voltage ( $V_{\rm DD}$ ) and load capacitance ( $C_{\rm L}$ ) on the Miller capacitance ( $C_{\rm MIL}$ ) which is formed by B2BT tunneling has been investigated. Several parameters for digital applications are computed and listed for inverter based on DG TFET. To carry out the transient analysis, a 4 ns time period digital pulse ( $V_{\rm in}$ ) is applied at the input of DG TFET inverter and output digital waveform is measured at node  $V_{\rm out}$ . Figure 7 has shown the Vout for various  $C_{\rm L}$  in order to evaluate the inverter performance in terms of rise time ( $T_{\rm r}$ ), fall time ( $T_{\rm f}$ ), delay (t), peak overshoot ( $V_{\rm p}$ ), % peak overshoot, miller capacitance ( $C_{\rm MIL}$ ). It is clearly seen from Table 2 and Fig. 7 that the % peak overshoots are diminishing from 42.8 to 2.14% and total delay increasing (0.18–1.9 ns) with increasing the  $C_{\rm L}$  (10–200 fF). This behavior can be explained by taking the impact of miller capacitance as given by Eqs (8 and 9). The extent of the voltage peak overshoot can be estimated from the

Fig. 7 Input and output waveforms of double gate TFET inverter for various capacitive load (CL)

| <b>Table 2</b> Impact of load capacitance $(C_L)$ on the transient performance of DGTFET |                     |                      |                            |            |            |                    |                       |

|------------------------------------------------------------------------------------------|---------------------|----------------------|----------------------------|------------|------------|--------------------|-----------------------|

| V <sub>DD</sub><br>0.7 V                                                                 | C <sub>L</sub> (fF) | Rise time $T_r$ (ns) | Fall time $T_{\rm f}$ (ns) | Delay (ns) | $V_{p}(V)$ | (%V <sub>p</sub> ) | C <sub>MIL</sub> (fF) |

| 1                                                                                        | 10                  | 0.2                  | 0.16                       | 0.18       | 0.30       | 42.80              | 11.27                 |

| 2                                                                                        | 50                  | 0.60                 | 0.55                       | 0.575      | 0.08       | 11.42              | 6.45                  |

| 3                                                                                        | 100                 | 1.2                  | 1.0                        | 1.1        | 0.04       | 5.71               | 6.06                  |

| 4                                                                                        | 150                 | 1.4                  | 1.5                        | 1.45       | 0.025      | 3.57               | 5.55                  |

| 5                                                                                        | 200                 | 2                    | 1.8                        | 1.9        | 0.015      | 2.14               | 4.32                  |

**Table 2** Impact of load capacitance  $(C_x)$  on the transient performance of DGTEE

following equations based on the law of charge conservation (Eqs. 6 and 7) [55, 56].

$$C_{\text{MIL}} \cdot (V_{\text{M}} - V_{\text{DD}}) + C_{\text{L}} \cdot V_{\text{M}} = V_{\text{DD}} \cdot (C_{\text{MIL}} + C_{\text{L}})$$

(8)

$$V_{\rm p} = V_{\rm M} - V_{\rm DD} = C_{\rm MIL} \cdot V_{\rm DD} / (C_{\rm MIL} + C_{\rm L}) \tag{9}$$

where  $C_{\rm MIL}$  denotes the Miller capacitance across drain and gate nodes consisting of both comprising inverter structure with N DGTFET and P DGTFET,  $C_L$  represents the load capacitance connected externally, maximum output voltage ( $V_{\rm out}$ ) represented by  $V_{\rm M}$ ,  $V_{\rm P}$  is the output peak overshoot voltage, and  $V_{\rm DD}$  is the supply voltage. In silicon-based TFETs, these equations clearly demonstrate the effect of  $C_{\rm MIL}$  on  $V_{\rm p}$ . Increasing load capacitance ( $C_{\rm L}$ ) raises the time constant ( $R_{\rm C}$ ), and thus increases the drain node's charge and discharge time in accordance with Eq. 10. This

effect can be validated in Fig. 7 and the parameters are shown in Table 2, showing that the delay increases with the  $C_L$ .

$$V = V_{\rm o} \left( 1 - e^{-t/RC_L} \right) \tag{10}$$

At the same instant, it is also observed that voltage peak overshoot occurs in the transient performance of the TFET inverter for each capacitance load. Figure 7 shows the diminishing voltage peak overshoots with an increasing load capacitance. The % peak overshoots are directly proportional to  $C_{\rm MIL}$ . Table 2 has listed the values of  $C_{\rm MIL}$  for various  $C_{\rm L}$ . The charge conservation equations (Eqs. 8 and 9) are applied to compute the value of  $C_{\rm MIL}$  (listed in Table 2) and it is found that the miller capacitance ( $C_{\rm MIL}$ ) decreases (11.27–4.32 fF) with increasing  $C_{\rm L}$  (10–200 fF), hence results in diminishing % peak overshoots. From the detailed discussion, it can be understood that to diminish the % peak overshoots, the higher values of load capacitance need to be considered so that impact of  $C_{\rm MIL}$  gets diminished in FTETs.

Figure 8 shows the impact of  $V_{\rm DD}$  on the Miller Capacitance ( $C_{\rm MIL}$ ). The transient performance of DGTFET inverter is listed in Table 3 has listed its performance parameters. Upon increasing the  $V_{\rm DD}$ , the delay of the inverter decreases, and shows saturation in delay for  $V_{\rm DD}$  from 0.6 to 0.8 V. Increasing  $V_{\rm DD}$  results in higher drain current, but for higher drain voltages, the drain current gets saturated as shown in Fig. 2a. From Table 3, it is clearly seen that the delay has decreased by 50% (from 0.8 to 0.4 ns) for  $V_{\rm DD}$  from 0.5 to 0.6 V, 37.5% (from 0.4 to 0.25 ns) for  $V_{\rm DD}$  from 0.6 to 0.7 V, and by 20% (0.25–0.2 ns) for  $V_{\rm DD}$  from 0.7 to 0.8 V, respectively. It is also observed that a 50% decrease in delay for the  $V_{\rm DD}$  from 0.5 to 0.6 V and only

Fig. 8 Input and output waveforms of double gate TFET inverter at various drain to source voltage  $(V_{\rm ds})$

| $C_{\rm L} = 15  \rm fF$ | $\begin{vmatrix} V_{\rm DD} \ (V_{\rm DD} = \\ V_{\rm in}) \end{vmatrix}$ | Rise time $T_r$ (ns) | Fall time $T_{\rm f}$ (ns) | Delay<br>(ns) | <i>V</i> <sub>p</sub> (V) | (%V <sub>p</sub> ) | C <sub>MIL</sub> (fF) |

|--------------------------|---------------------------------------------------------------------------|----------------------|----------------------------|---------------|---------------------------|--------------------|-----------------------|

| 1                        | 0.5                                                                       | 0.8                  | 0.8                        | 0.8           | 0.175                     | 35                 | 8                     |

| 2                        | 0.6                                                                       | 0.4                  | 0.4                        | 0.4           | 0.2                       | 33                 | 7.5                   |

| 3                        | 0.7                                                                       | 0.25                 | 0.25                       | 0.25          | 0.22                      | 31.4               | 6.88                  |

| 4                        | 0.8                                                                       | 0.2                  | 0.2                        | 0.2           | 0.21                      | 26.25              | 5.35                  |

**Table 3** Impact of  $V_{DD}$  on the transient performance of DGTFET

20% decrease in delay for  $V_{\rm DD}$  from 0.7 to 0.8 V due to saturation of drain current at higher drain voltages.

An opposite trend is observed for the % peak overshoot; %  $V_{\rm p}$  does not show significant variation for  $V_{\rm DD}$  from 0.5 to 0.6 V, it only changes from 35 to 33%. However, for the  $V_{\rm DD}$  range from 0.7 to 0.8 V, there is a significant variation in %  $V_{\rm p}$  are noticed during the simulations from 31.4 to 26.25%. Simulations results also investigated that miller capacitance ( $C_{\rm MIL}$ ) continuously decreasing from 8 to 5.35 fF for increasing the  $V_{\rm DD}$  from 0.5 to 0.8 V and this impact is also noticed in the % peak voltage overshoots from 35 to 26.25% which further results in better delay performance of TFET inverter (see Fig. 8 and Table 3).

#### 4 Conclusion

Simulations results investigate that the quantum band to band tunneling (B2BT) charge transport process is responsible for current conduction in DGTFETs producing steep subthreshold swing (SS ~ 15 mV/dec) and high  $I_{\rm ON}/I_{\rm OFF}$  ratio ~10<sup>11</sup> with the presence of very low leakage current (~5 × 10<sup>-14</sup> A/ $\mu$ m), and thus can be considered for low-power applications. Implementation of I–V/C–V data sets in the form look table coded with verilog-A model can be considered as one of the effective way to analyze circuit behavior of DGTFETs device structure. Simulation results for GBP, TFP, transit time ( $t_r$ ),  $g_m$ ,  $f_T$  investigate that the DGTFET device structure can be considered for analog applications. Findings from transient analysis describe the existence of miller capacitance ( $C_{\rm MIL}$ ) present at gate-drain node of TFET inverter, which is affected by voltage ( $V_{\rm DD}$ ) and load capacitance ( $C_{\rm L}$ ). The combined study of analog and transient parameters of TFET device structure describes the suitability of TFET for integrated circuits applications.

### References

1. Baravelli, E., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: TFET inverters with n-/p-devices on the same technology platform for low-voltage/low-power applications. IEEE Trans. Electron Devices **61**(2), 473–478 (2014)

- Nikonov, D.E., Young, I.A.: Overview of beyond-CMOS devices and a uniform methodology for their benchmarking. Proc. IEEE 101(12), 2498–2533 (2013)

- 3. Nikonov, D.E., Young, I.A.: Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits. IEEE J. Explor. Solid-State Comput. Devices Circuits 1, 3–11 (2015)

- Pan, C., Naeemi, A.: An expanded benchmarking of beyond-CMOS devices based on Boolean and neuromorphic representative circuits. IEEE J. Explor. Solid-State Comput. Devices Circuits 3, 101–110 (2017)

- 5. Lu, H., Paletti, P., Li, W., Fay, P., Ytterdal, T., Seabaugh, A.: Tunnel FET analog benchmarking and circuit design. IEEE J. Explor. Solid-State Comput. Devices Circuits 4(1), 19–25 (2018)

- 6. Guenifi, N., Rahi, S.B., Ghodbane, T.: Rigorous study of double gate tunneling field effect transistor structure based on silicon. Mater. Focus. 7(6), 866–872 (2018)

- Kumar, D.: Performance evaluation of double gate tunnel FET based chain of inverters and 6-T SRAM cell. Eng. Res. Express. 1(2), 025055 (2019)

- 8. Chen, S., Liu, H., Wang, S., Li, W., Wang, X., Zhao, L.: Analog/RF performance of T-shape gate dual-source tunnel field-effect transistor. Nanoscale Res. Lett. 13(1), 321 (2018)

- Der Agopian, P.G., Martino, J.A., Vandooren, A., Rooyackers, R., Simoen, E., Thean, A., Claeys, C.: Study of line-TFET analog performance comparing with other TFET and MOSFET architectures. Solid-State Electron. 128, 43–47 (2017)

- Baravelli, E., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: TFET inverters with n-/p-devices on the same technology platform for low-voltage/low-power applications. IEEE Trans. Electron Devices 61(2), 473–478 (2014)

- Khatami, Y., Banerjee, K.: Steep subthreshold slope n-and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 56(11), 2752–2761 (2009)

- 12. Zhuge, J., Verhulst, A.S., Vandenberghe, W.G., Dehaene, W., Huang, R., Wang, Y., Groeseneken, G.: Digital-circuit analysis of short-gate tunnel FETs for low-voltage applications. Semicond. Sci. Technol. **26**(8), 085001 (2011)

- Bizindavyi, J., Verhulst, A.S., Verreck, D., Sorée, B., Groeseneken, G.: Large Variation in Temperature Dependence of Band-to-Band Tunneling Current in Tunnel Devices. IEEE Electron Device Lett. 40(11), 1864–1867 (2019)

- 14. Wu, P., Appenzeller, J.: Reconfigurable black phosphorus vertical tunneling field-effect transistor with record high on-currents. IEEE Electron Device Lett. **40**(6), 981–984 (2019)

- Verhulst, A.S., Vandenberghe, W.G., Maex, K., De Gendt, S., Heyns, M.M. and Groeseneken,

G.: Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. IEEE

Electron Device Lett. 29(12), 398–1401 (2008)

- 16. Kim, S.W., Choi, W.Y., Sun, M.C., Kim, H.W. and Park, B.G.: Design guideline of Si-based L-shaped tunneling field-effect transistors. Jpn. J. Appl. Phys., 51(6S), 06FE09 (2012)

- 17. Mookerjea, S., Datta, S.: Comparative study of Si, Ge and InAs based steep subthreshold slope tunnel transistors for 0.25 V supply voltage logic applications. In: 2008 Device Research Conference, pp. 47–48. IEEE (2008)

- 18. Gandhi, R., Chen, Z., Singh, N., Banerjee, K., Lee, S.: Vertical Si-Nanowire \$ n \$-Type Tunneling FETs With Low Subthreshold Swing (\$\leq\hbox \{50}\\hbox mV/decade \$) at Room Temperature. IEEE Electron Device Lett. **32**(4), 437–439 (2011)

- Asthana, P.K., Goswami, Y., Basak, S., Rahi, S.B., Ghosh, B.: Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. RSC Adv. 5(60), 48779–48785 (2015)

- Luo, Z., Wang, H., An, N., Zhu, Z.: A tunnel dielectric-based tunnel FET. IEEE Electron Device Lett. 36(9), 966–968 (2015)

- Rahi, S.B., Bahniman, G.: High-k Double Gate Junctionless Tunnel FET with Tunable Bandgap. RSC Adv. 5(67), 54544–54550 (2015) (Impact factor: 3.049). https://doi.org/10. 1039/C5RA06954H

- Rahi, S.B., Asthana, P. Gupta, S.: Heterogate junctionless tunnel field-effect transistor: future of low-power devices. J. Comput. Electron. 16(1), 30–38 (2017) (Impact factor: 1.637). https://doi.org/10.1007/s10825-016-0936-9

Wang, X., Tang, Z., Cao, L., Li, J., Liu, Y.: Gate Field plate structure for subthreshold swing improvement of Si line-tunneling FETs. IEEE Access 7, 100675–100683 (2019)

- Lu, H., Paletti, P., Li, W., Fay, P., Ytterdal, T. and Seabaugh, A.: Tunnel FET analog benchmarking and circuit design. IEEE J. Explor. Solid-State Comput. Devices Circuits 4(1), 19–25 (2018)

- 25. Strangio, S., Settino, F., Palestri, P., Lanuzza, M., Crupi, F., Esseni, D., Selmi, L.: Digital and analog TFET circuits: design and benchmark. Solid-State Electron. **146**, 50–65 (2018)

- Kim, M.S., Liu, H., Li, X., Datta, S., Narayanan, V.: A steep-slope tunnel FET based SAR analog-to-digital converter. IEEE Trans. Electron Devices 61(11), 3661–3667 (2014)

- Elnaggar, M., Shaker, A., Fedawy, M.: Modified hetero-gate-dielectric TFET for improved analog and digital performance. In: 2018 13th International Conference on Computer Engineering and Systems (ICCES), pp. 683–687. IEEE (2018)

- 28. Imenabadi, R.M., Saremi, M., Vandenberghe, W.G.: A novel PNPN-like Z-shaped tunnel field-effect transistor with improved ambipolar behavior and RF performance. IEEE Trans. Electron Devices **64**(11), 4752–4758 (2017)

- Asra, R., Shrivastava, M., Murali, K.V., Pandey, R.K., Gossner, H., Rao, V.R.: A tunnel FET for \$ V\_ {DD} \$ scaling below 0.6 V with a CMOS-comparable performance. IEEE Trans. Electron Devicesy 58(7), 1855–1863 (2011)

- Datta, S., Liu, H., Narayanan, V.: Tunnel FET technology: a reliability perspective. Microelectron. Reliab. 54(5), 861–874 (2014)

- 31. Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. **28**(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

- 32. Ionescu, A.M., Riel, H.: Tunnel field-effect transistor as energy-efficient electronic switches. Nature 479(7373), 329–337 (2011). https://doi.org/10.1038/nature10679

- 33. Mookerjea, S., Krishnan, R., Datta, S., Narayanan, V.: Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans. Electron Devices **56**(9), 2092–2098 (2009)

- 34. Nirschl, T., Wang, P.F., Weber, C., Sedlmeir, J., Heinrich, R., Kakoschke, R., Schrufer, K., Holz, J., Pacha, C., Schulz, T., Ostermayr, M.: The tunneling field effect transistor (TFET) as an add-on for ultra-low-voltage analog and digital processes. In: IEDM Technical Digest. IEEE International Electron Devices Meeting, pp. 195–198. IEEE (2004)

- 35. Kumar, D., Jain, P.: Performance of dual metal-double gate tunnel field effect transistor with different dielectrics. In: Proceeding of International Conference on Intelligent Communication, Control and Devices 2017, pp. 927–933. Springer, Singapore

- 36. Mallik, A., Chattopadhyay, A.: Drain-dependence of tunnel field-effect transistor characteristics: the role of the channel. IEEE Trans. Electron Devices **58**(12), 4250–4257 (2011)

- 37. Xing, H.G., Zhou, G., Li, M., Lu, Y., Li, R., Wistey, M., Fay, P., Jena, D., Seabaugh, A.: Tunnel FETs with tunneling normal to the gate. In: 2013 Third Berkeley Symposium on Energy Efficient Electronic Systems (E3S), pp. 1–1. IEEE (2013)

- 38. Sedighi, B., Hu, X.S., Liu, H., Nahas, J.J., Niemier, M.: Analog circuit design using tunnel-FETs. IEEE Trans. Circuits Syst. I Regul. Pap. 62(1), 39–48 (2014)

- 39. Narang R, Saxena M, Gupta RS, Gupta M. Device and circuit level performance comparison of tunnel FET architectures and impact of heterogeneous gate dielectric. JSTS: J. Semicond. Technol. Sci. 13(3), 22436 (2013)

- Saripalli, V., Datta, S., Narayanan, V., Kulkarni, J.P.: Variation-tolerant ultra low-power heterojunction tunnel FET SRAM design. In: Proceedings of the 2011 IEEE/ACM International Symposium on Nanoscale Architectures, 2011 Jun 8, pp. 45–52. IEEE Computer Society (2011)

- Lee, Y, Kim, D., Cai, J., Lauer, I., Chang, L., Koester, S.J., Blaauw, D., Sylvester, D.: Low-power circuit analysis and designbased on heterojunction tunneling transistors (HETTs). IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 21(9), 1632–1643 (2013)

- 42. Avci, U.E., Morris, D.H., Hasan, S., Kotlyar, R., Kim, R., Rios, R., Nikonov, D.E., Young, I.A.: Energy efficiency comparison of nanowire heterojunction TFET and Si MOSFET at Lg

- = 13nm, including P-TFET and variation considerations. In: 2013 IEEE International Electron Devices Meeting, 2013 Dec 9, pp. 33–4. IEEE (2013)

- 43. Trivedi, A.R., Carlo, S., Mukhopadhyay, S.: Exploring tunnel-FET for ultra low power analog applications: a case study on operational transconductance amplifier. In: Proceedings of the 50th Annual Design Automation Conference, 2013 May 29, p. 109. ACM (2013)

- 44. Raghav, N., Bansal, M.: Analysis of power efficient 6-T SRAM cell with performance measurements. In: 2017 International Conference on Innovations in Control, Communication and Information Systems (ICICCI), 2017 Aug 12, pp. 1–4. IEEE (2017)

- Palomo, F.R., Fernández-Martínez, P., Mogollón, J.M., Hidalgo, S., Aguirre, M.A., Flores, D., López-Calle, I., de Agapito, J.A.: Simulation of femtosecond pulsed laser effects on MOS electronics using TCAD Sentaurus customized models. Int. J. Numer. Model. Electron. Networks Devices Fields 23(4–5), 379–399 (2010)

- Anand, S., Amin, S.I., Sarin, R.K.: Analog performance investigation of dual electrode based doping-less tunnel FET. J. Comput. Electron. 15(1), 94–103 (2016)

- 47. Yang, Y., Tong, X., Yang, L.T., Guo, P.F., Fan, L., Yeo, Y.C.: Tunneling field-effect transistor: Capacitance components and modeling. IEEE Electron Device Lett. **31**(7), 752–754 (2010). https://doi.org/10.1109/LED.2010.2047240

- 48. Mookerjea, S., Krishnan, R., Datta, S., Narayanan, V.: On enhanced Miller capacitance effect in interband tunnel transistors. IEEE Electron Device Lett.

- Biswas, A., Dan, S.S., Le Royer, C., Grabinski, W., Ionescu, A.M.: TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model. Microelectron. Eng. 1(98), 334–337 (2012)

- 50. Knoch J.: Optimizing tunnel FET performance-Impact of device structure, transistor dimensions and choice of material. In: 2009 International Symposium on VLSI Technology, Systems, and Applications, 2009 Apr 27, pp. 45–46. IEEE (2009)

- 51. Singh, K.S., Kumar, S., Nigam, K., Tikkiwal, V.A.: Tunnel field effect transistor for ultra low power applications: a review. In: 2019 International Conference on Signal Processing and Communication (ICSC), 2019 Mar 7, pp. 286–291. IEEE (2019)

- 52. Wang, P.Y., Tsui, B.Y.: Investigation into gate-to-source capacitance induced by highly efficient band-to-band tunneling in p-channel Ge epitaxial tunnel layer tunnel FET. IEEE Trans. Electron Devices **63**(4), 1788–1790 (2016)

- 53. Jain, P., Kumar, D.: Drive current boosting using pocket implant near to the strained SiGe/Si source with single-metal/dual-metal double-gate tunnel field-effect transistor. In: Proceeding of International Conference on Intelligent Communication, Control and Devices, pp. 943–950. Springer, Singapore (2017)

- Kumar, D., Jain, P.: Double gate tunnel field effect transistor with extended source structure and impact ionization enhanced current. Inintell. Commun., Control. Devices, pp. 973–980. Springer, Singapore (2018)

- Mookerjea, S., Krishnan, R., Datta, S., Narayanan, V.: Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation. IEEE Trans. Electron Devices 56(9), 2092–2098 (2009)

- Shoji, M.: CMOS digital circuit technology. In: Englewood Cliffs, ch. 4, pp. 189–190. Prentice-Hall, NJ (1988)