Copyright © 2018 by American Scientific Publishers All rights reserved. Printed in the United States of America

# **Rigorous Study of Double Gate Tunneling Field Effect Transistor Structure Based on Silicon**

N. Guenifi<sup>1,\*</sup>, S. B. Rahi<sup>2</sup>, and T. Ghodbane<sup>1</sup>

<sup>1</sup>LEA Electronics Department, University Mostefa Benboulaid of Batna 2, Batna (05000) Algeria <sup>2</sup>Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur 208016, India

## ABSTRACT

Increased static and dynamic power dissipation in the integrated circuits (ICs) are the main obstacle for growing demands of smart phones and laptops, which require semiconductor devices having low power operation. As the conventional MOSFET has a thermodynamic limit of 60 mV/decade at 300 K on subthreshold slope (SS), so the device based on the mechanism other than diffusion over a thermal barrier came into existence. In this regard, Tunnel-FET (TFET) has emerged as a promising replacement. Due to its lower subthreshold slope (<60 mV/decade at 300 K), reduced OFF-current ( $I_{OFF}$ ), reduced power consumption, and negligible short channel effects, TFETs have achieved a lot of attention in the recent years. In the present research work, double-gate TFET (DG-TFET) device has been investigated. The simulation result shows a very good  $I_{ON}/I_{OFF}$  ratio (10<sup>12</sup>) and low SS (~41.54 mV/dec). The DG-TFET has very low off current,  $I_{OFF}$  (~10<sup>-17</sup> A/ $\mu$ m) and ON-current of ( $I_{ON}$ ) ~10<sup>-5</sup> (A/ $\mu$ m) using gate bias in the vicinity of 0.5. In addition, we have optimized the device parameters, thus improving the  $I_{ON}$  current and the  $I_{ON}/I_{OFF}$  ratio yield for two kinds of technologies (using HfO<sub>2</sub> or SiO<sub>2</sub> as gate dielectric). A comparison between the two technologies was made. Gate to drain ( $C_{gd}$ ) capacitance as function of gate to source voltage  $V_{GS}$  as well as drain to source voltage  $V_{DS}$  at frequency f = 1 MHz,  $C_{gd}$  is weaker using SiO<sub>2</sub> as gate dielectric compared to HfO<sub>2</sub>.

**KEYWORDS:** Tunnel FET, High-κ Dielectric, Subthreshold Slope (SS), Band-to-Band Tunneling (BTBT), Quantum Mechanical Transport QMT.

# **1. INTRODUCTION**

The inability, to reduce power density with each progressive technology node has been a dominant constraint for modern semiconductor players. Various techniques have been proposed to reduce computational power spanning from the architecture level to the fundamental semiconductor device level are being actively explored. Tunnel Field-effect transistors (TFETs), based on band-to-band tunneling (BTBT), a quantum mechanical transport (QMT) phenomenon has gained a lot of attention in the modern research community due to its potential for reducing power dissipation for advanced integrated circuits (ICs). This ever increasing interest owes to their feasibility to overcome the 60 mV/dec subthreshold slope limitation of the standard MOSFETs,<sup>1-4</sup> as well as compatibility.<sup>5</sup> TFET is basically a p-i-n structured device. The device operation requires reverse bias to realize tunneling phenomenon between sources and drain regions with a sufficient level of gate voltage.6-12

\*Author to whom correspondence should be addressed.

Accepted: xx Xxxx xxxx

Mater. Focus 2018, Vol. 7, No. xx

2169-429X/2018/7/001/007

Recently, many research groups across the world have reported many proposed devices designed to overcome the on-state current limitation in TFET. The double gate TFET (DG-TFET) with high- $\kappa$  dielectric is an effective way to improve the on-current ( $I_{\rm ON}$ ), while taking advantage of steeper subthreshold slope and lower OFF-current.<sup>12–23</sup>

# 2. ANALYTIC ANALYSIS OF SENSITIVITY

For MOSFETs, the analytic expression for current in a subthreshold regime, where most of current modulation as a function of gate voltage occurs, is given approximately by:<sup>12</sup>

$$I_{\rm DS} = I_{\rm OFF} \exp\left(\frac{V_{\rm G}}{V_{\rm th}(1 + (C_{\rm S}/C_{\rm OX}))}\right) \tag{1}$$

where  $V_{\rm th}$  equals kT/q and  $I_{\rm OFF}$  is the OFF current at  $V_{\rm G} = 0$ .  $C_{\rm S}$  represents the semiconductor capacitance and it is a function of  $\varepsilon_{\rm ch}$  and  $t_{\rm ch}$  for short-channel devices.

In case of TFETs, the approximate equation for the I-V characteristics leads as follows:<sup>12</sup>

$$I_{\rm DS} = I_{\rm OFF} \exp\left(A\sqrt{m^*} \left(\sqrt{E_{\rm g} + qV_{\rm G} - \sqrt{E_{\rm g}}}\right)\right) \quad (2)$$

Email: guenifi\_2000@yahoo.fr

Received: xx Xxxx xxxx

Rigorous Study of Double Gate Tunneling Field Effect Transistor Structure Based on Silicon

Guenifi et al.

where A is the total tunneling distance which is the sum of natural scaling length  $\lambda$  and source depletion width  $W_{\rm D}$  ( $A = \lambda + W_{\rm D}$ ), q is the unit charge and  $E_{\rm g}$  and  $m^*$  are bandgap and effective mass of the channel material, respectively.

The subthreshold swing of a device is defined as: the change in gate voltage which must be applied in order to create a one decade increase in the output  $current^{6, 12}$

$$S = \frac{dV_{\rm GS}}{d(\log I_{\rm DS})} (\rm mV/dec)$$

(3)

That the tunneling probability, T(E) is given by:<sup>12</sup>

$$T(E) \propto \left( -\frac{4\sqrt{2m^* E_g^{3/2}}}{3\lfloor e \rfloor \bar{h}(E_g + \Delta \Phi)} \sqrt{\frac{\varepsilon_{si}}{\varepsilon_{ox}} t_{ox} t_{si}} \right) \Delta \Phi \quad (4)$$

In Eq. (4),  $m^*$  is the electron effective mass,  $E_g$  is band gap,  $\Delta \Phi$  is the energy range over which tunneling can take place, and  $t_{ox}$ ,  $t_{si}$ ,  $\varepsilon_{ox}$ ,  $\varepsilon_{si}$  are the oxide and silicon films thickness and dielectric constants respectively, and  $\bar{h}$  is the reduced Planck's constant. The tunneling window ( $\Delta \Phi$ ) in the tunneling probability is written as follows:<sup>12</sup>

$$\Delta \Phi = E_{\rm V}^{\rm ch} - E_{\rm C}^{\rm S}$$

# 3. STRUCTURE AND SIMULATION METHODOLOGY

The electrical performance of DG-TFET was investigated using Silvaco TCAD Atlas 2D software V5.15.32 R.<sup>10</sup>

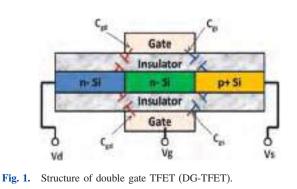

The double gate provides electrostatic control over the channel in which the drain field line cannot affect or disturb the source-to-channel barrier and it promisingly reduces the short channel effects. The DG-TFET, adopted in the present research work is shown in Figure 1, having three regions: *n*-type semiconductor bar forming source and channel region, and *p*-type semiconductor by forming drain region. In between two regions an intrinsic semiconductor layer is sandwich. The quantum mechanical transistor (QMT) has reached such small dimensions for doping concentration gradients are:  $7.5 \times 10^{20}$  cm<sup>-3</sup>,  $10^{10}$  cm<sup>-3</sup> and  $5 \times 10^{18}$  cm<sup>-3</sup> for the source, intrinsic, and drain regions respectively. Doping has been optimized to create the maximum ON-current ( $I_{ON}$ ), while keeping OFF-current ( $I_{OFF}$ ) low. In order to have a minimal  $I_{OFF}$ , the

ARTICLE

Fig. 2. Atlas resolution algorithm of double gate TFET.

doping of the source is slightly lower compared to that of the drain.

The flow chart for present research work is shown in Figure 2.

Fig. 3. Tony plot display using 2D mesh of double gate TFET.

Mater. Focus, 7, 1–7, 2018

| Parameters                                        | Values                               |

|---------------------------------------------------|--------------------------------------|

| Gate length $(L_{\sigma})$                        | 50 nm                                |

| Drain and source lengths $(L_{\rm D}, L_{\rm S})$ | 100 nm                               |

| Oxide thicknees $(t_{ox})$                        | 2 nm                                 |

| Channel thicknees $(t_{si})$                      | 10 nm                                |

| Source concentration $(N_a)$                      | $7.5 \times 10^{20} \text{ cm}^{-3}$ |

| Intrinsic concentration $(N_d)$                   | $10^{10} \text{ cm}^{-3}$            |

| Drain concentration $(N_{\rm d})$                 | $5 \times 10^{18} \text{ cm}^{-3}$   |

| Gate voltage $(V_{\sigma})$                       | 1.0 V                                |

| Supply voltage $(V_{dd})$                         | 0.5 V                                |

Table II.

Parameters oxide gate used in simulation.

|                                               |                  | Oxide gate                  |               |                  |  |

|-----------------------------------------------|------------------|-----------------------------|---------------|------------------|--|

| Parameters                                    | SiO <sub>2</sub> | $\mathrm{Si}_3\mathrm{N}_4$ | $ZrO_2$       | HfO <sub>2</sub> |  |

| Bandgap (eV)<br>Relative dielectrics constant | 9<br>3.9         | 5.3<br>7.9                  | 5.7–5.8<br>22 | 4.5–6<br>25      |  |

The DG-TFET, as shown in Figure 1, consists of p+ source, intrinsic channel and n+ drain. The local tunneling models were used to calculate tunneling current from the source to drain with varying gate voltage ( $V_{GS}$ ).

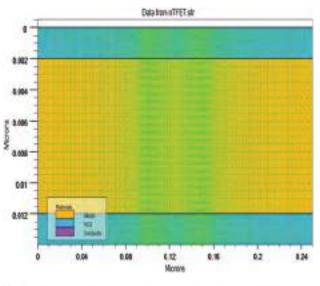

The I-V characteristics of DG-TFET have been plotted and investigated by using Newton method to solve numerical system. The choice of the mesh under atlas is a vital step to have a convergence. Figure 3 shows the tony plot display using 2D mesh of DG-TFET.

The gate dielectric layer must be sufficiently thin and therefore, we have taken the oxide thickness  $t_{ox}$  of 2 nm. The work function of the metal work function,  $\Phi_M$  used is 5.2 eV. The drain, source and intrinsic region lengths,  $L_D$ ,  $L_S$  and  $L_G$  are taken as: 100 nm, 100 nm and 50 nm

Fig. 4. Energy band-diagram (a) at  $V_{\rm GS}=0.0~{\rm V}$  (OFF-state) for DG-TFET.

respectively. The silicon thickness  $t_{Si}$  is 10 nm for DG-TFET. All the physical parameters use in work is tabulated in Table I. The electrical parameters of used dielectric materials is shown in Table II.<sup>19–21</sup>

### 4. RESULTS AND DISCUSSION

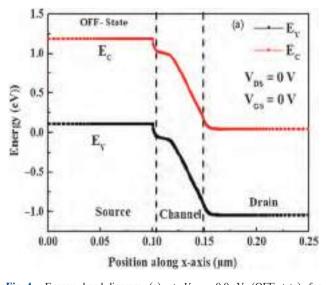

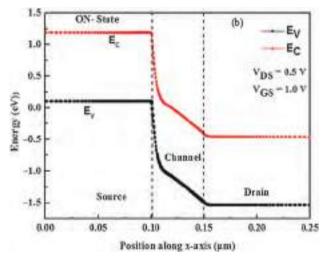

Using 2-D numerical device simulator, the electrostatic performance of DG-TFET is analyzed. Figures 4 and 5 show the simulated energy band diagram of DG-TFET, shown in Figure 1. With the help of the energy band diagram the ON–OFF state conduction phenomenon of the DG-TFET is explained. As shown in Figures 4 and 5, when  $V_{\rm GS} = 0.0$  V and  $V_{\rm DS} = 0.0$  V. The device is in OFF-state with very large tunnel barrier width, and therefore the electrons do not have enough energy to move from the valance band of the source to the conduction band of the channel. On application of sufficiently high gate voltage

**Fig. 5.** Energy band-diagram at  $V_{GS} > 0.0$  V (ON-state) for DG-TFET.

# ARTICLE

Fig. 7. Potential surface for DG-TFET structure for  $V_{\rm GS} = 0.0$  V and  $V_{\rm GS} = 1.0$  V.

(i.e.,  $V_{GS} = 0.5$  V and  $V_{DS} = 1.0$  V), the width of tunneling barrier is reduced and the device switches to ON-state.

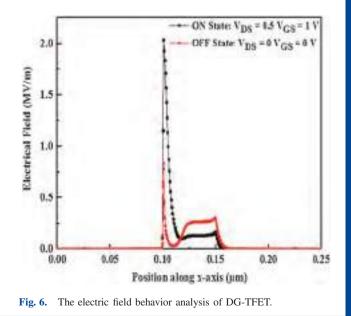

When the device switched from the OFF-state to the ON-state, an increase in the electric field is observed. It has

VDS = 0.5 V

tox = 2 nm

ZrO<sub>2</sub>

HIO,

SINA

SiO<sub>1</sub>

0.5

$V_{DS} = 0.5 V$

tox - 2 mm

0.5

1.0

1.5

Gate Voltage (V)

2.0

2.5

ZrO<sub>2</sub>

HIO2

SI<sub>1</sub>N<sub>4</sub>

SiO2

25

3.0

3.0

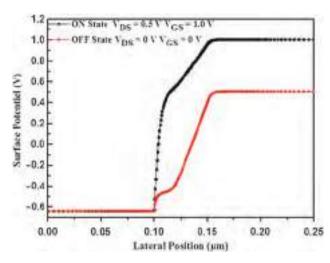

been observed that, the tunnel width decreases and there is a shift of the conduction band downwards. Thus, the gradual enhancement of the gate bias degrades the barrier width and causes an increased tunneling of carriers, indicated in Figure 5. Figures 6 and 7 shows the internal electric filed and surface potential inside the device. In both (Figs. 6 and 7), there is relative comparison between ON and OFF-state.

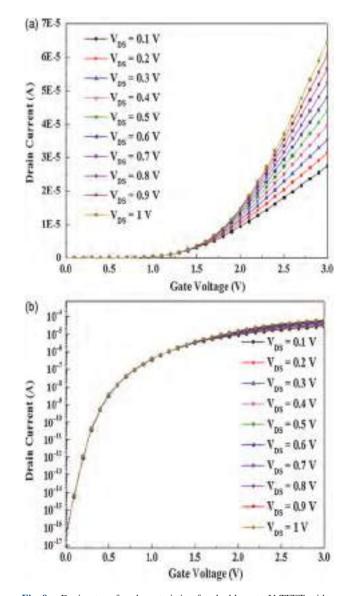

Since, HfO<sub>2</sub> is the core material in the gate stack in high- $\kappa$  metal gate devices for technology nodes less than 45 nm,<sup>22, 23</sup> therefore we have used it in our device simulations. Figure 8 shows the transfer characteristic of DG-TFET. As shown in Figures 9((a) linear (b)) semilog plot), the variation of leakage current ( $I_{OFF}$ ) is almost constant for all values of  $V_{DS}$ .

Fig. 8. Plot of the transfer characteristic  $(I_{\rm DS}-V_{\rm GS})$ , regarding different gate oxide in Atlas of a DG-TFET device with  $L_{\rm G} = 50$  nm (a) linear (b) plot Semilog plot.

1.5

Gate Voltage (V)

2.0

1.0

**Fig. 9.** Device transfer characteristics for double gate N-TFET with a variation of  $V_{\rm DS}$  (a) plot linear (b) plot Semilog.

(a) 6E-5

Drain Current (A/µm)

(b) 1E-05

Drain Current (A/µm

5E-5

4E-5

3E-5

2E-5

1E-5

1E-06

1E-07

1E-08

1E-09

1E-10

1E-11

1E-12

1E-13

1E-14

1E-15

1E-16

0.0

0.0

| Table III.         Lists of the computed electrical parameters of the DG-TFET |                        |                        |                         |                        |  |  |  |

|-------------------------------------------------------------------------------|------------------------|------------------------|-------------------------|------------------------|--|--|--|

|                                                                               |                        | Oxide gate             |                         |                        |  |  |  |

| Parameters                                                                    | ZrO <sub>2</sub>       | $HfO_2$                | ${\rm Si_3N_4}$         | $SiO_2$                |  |  |  |

| V <sub>th</sub> (V)                                                           | 0.2                    | 0.2                    | 0.45                    | 0.5                    |  |  |  |

| SS<br>(mV/decade)                                                             | 41.59                  | 41.54                  | 43.99                   | 46.89                  |  |  |  |

| $I_{\rm ON}$ (A/ $\mu$ m)                                                     | $5.26 	imes 10^{-5}$   | $4.38 \times 10^{-5}$  | $5.84 	imes 10^{-6}$    | $1.118 \times 10^{-6}$ |  |  |  |

| $I_{\rm OFF}$ (A/ $\mu$ m)                                                    | $5.02 	imes 10^{-17}$  | $4.03 	imes 10^{-17}$  | $2.52 	imes 10^{-17}$   | $2.43 	imes 10^{-17}$  |  |  |  |

| $I_{\rm ON}/I_{\rm OFF}$                                                      | $1,05 \times 10^{+12}$ | $1,09 \times 10^{+12}$ | $2,318 \times 10^{+11}$ | $4,61 \times 10^{+10}$ |  |  |  |

It is evident from the results that, the drain current performance is improving with replacement of high- $\kappa$  gate materials instead of using conventional SiO<sub>2</sub>. Threshold voltage  $(V_{tb})$  of DG-TFET reduces with high- $\kappa$  gate, as shown in Table III due to improved electrostatic filed inside tunneling region. This is also a scientific indication for lower power supply.

The output characteristic is improved with increasing drain voltage and achieves its optimum value for drain voltage  $V_{\rm DS}$  equal to 1.0 V. The use of high-high- $\kappa$ improves the output characteristics for a low gate voltage of the order of 0.5 V. An increase in the drain voltage  $V_{\rm DS}$  greatly increased  $I_{\rm ON}$  current but had no effect on the threshold voltage.

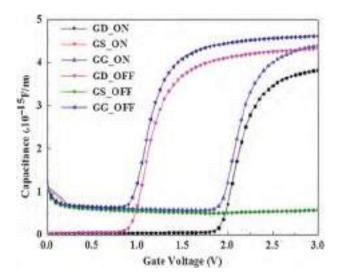

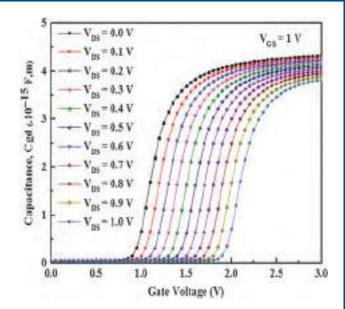

The various capacitance parameters such as gate-todrain  $(C_{gd})$ , gate-to-source  $(C_{gs})$  and drain-to-source  $(C_{ds})$ have been extracted from AC analysis of the designed structure. Figures 10 and 11 show the CV analysis results for DG-TFET. CV analysis of DG-TFET is done at 1 MHz frequency. It is observed that  $C_{\rm gd}$  increases with increasing gate voltage, this is due to the reduction of the potential barrier (as we saw in the energy band diagram, shown in Fig. 7).

Fig. 10. Capacitance voltage characteristics showing the gate  $(C_{gg})$ , gate to source  $(C_{gs})$ , and gate to drain  $(C_{gd})$  capacitance as function of gate to source  $V_{GS}$  for for DG-TFET extracted at f = 1 MHz.

Fig. 11. Gate-to-drain capacitance  $C_{\rm gd}$  as a function of gate to source voltage  $V_{GS}$  for different drain to source voltage  $V_{DS}$  for DGTFET extracted at f = 1 MHz.

Figure 10 shows comparison between available capacitance such as:  $(C_{gd})$ , gate-to-source  $(C_{gs})$  and drain-tosource  $(C_{ds})$ . The capacitance voltage (CV) characteristics showing the gate  $(C_{gg})$ , gate to source  $(C_{gs})$ , and gate to drain  $(C_{gd})$  capacitance as function of gate to source  $V_{GS}$ for for DG-TFET. Due to the presence of a source side tunnel barrier, the gate-to source capacitance  $(C_{gs})$  is very small. It explains that BTBT has negligible influence in the charge distribution of a DGTFET. While,  $C_{\rm gd}$  (gateto-drain capacitance) reflects the entire gate capacitance  $(C_{sg})$ . The  $C_{sd}$  decreases and shifts to the right when, the drain voltage  $(V_{DS})$  increases. This is due to the reduction of the tunnel distance as was observed on the energy bands, this observation was ensured by the simulation.

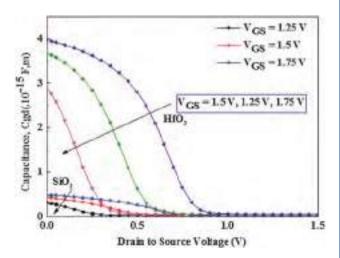

Fig. 12. Gate-to-drain capacitance  $C_{\rm gd}$  as a function of drain to source voltage  $V_{\rm DS}$  for different gate to source voltage  $V_{\rm GS}$  for DG-TFET extracted at f = 1 MHz (SiO<sub>2</sub> and HfO<sub>2</sub>).

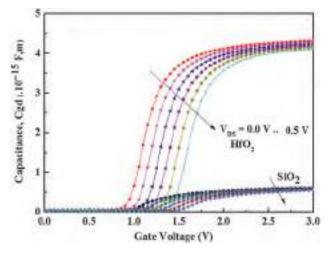

**Fig. 13.** Comparison between gate-to-drain capacitance  $C_{gd}$  as a function of drain to source voltage  $V_{GS}$  (SiO<sub>2</sub> and high- $\kappa$ ) for DG-TFET extracted at f = 1 MHz.

Figures 12 and 13 show CV characteristics of DG-TFET for  $SiO_2$  and  $HfO_2$  (as oxide gate).

In ON-state, changing Oxide Gate gives a smaller  $C_{gd}$ , inv when we use SIO<sub>2</sub> as oxide gate than high- $\kappa$  '(HfO<sub>2</sub>).  $C_{gd}$  is significantly reduced in the inversion region (a difference of 3 decades) despite there is not a big difference in the current (Fig. 8). In order to improve switching speed of DGTFET, we have to use the both oxide gate (HfO<sub>2</sub> and SiO<sub>2</sub>). The results are compared with those plotted in literature A good agreement is observed between both work.<sup>23</sup>

# 5. CONCLUSION

ARTIK

In this paper, we designed and analyzed the *n* type double gate tunnel Field Effect Transistor (DG-TFET), to address the requirements for ULP (Ultra-Low-Power) applications. The performance of the DG-TFET design in terms of power, the DG-TFET supports voltage scaling and works for supply voltage from 0.1 to 1.0 V. In this paper a double gate TFET (DG-TFET) electrical characteristics is investigated using the 2-D simulation with of standard scientific computing tool, Silvaco. The device electrical parameters such as drain current, and threshold voltage, subthreshold slope (SS), leakage current ( $I_{OFF}$ ),  $I_{ON}/I_{OFF}$  ratio have been obtained Threshold voltage of DG-TFET reduces due to improved electrostatic filed inside tunneling region. This is also a scientific indication for lower power supply.

It is evident from, the results that drain current is improving. Current,  $I_{\rm ON}$  it value very low close to  $10^{-5}$ and  $I_{\rm OFF}$  close to  $10^{-17}$  for the SiO<sub>2</sub> gate oxide and high- $\kappa$ (HfO<sub>2</sub>). The ratio  $I_{\rm on}/I_{\rm OFF}$  is very large, whatever the nature of the gate oxide, so SS is weak. Whatever the nature of the chosen oxide, this device gives excellent  $I_{\rm ON}/I_{\rm OFF}$  ratio of  $10^{12}$  for a very.

They have been consistent with other studies having noble information. The results for  $SiO_2$  oxide have been

improved. The CV characteristics of DG-TFET are also investigated.

### **References and Notes**

- P. Wang and B. Tsui, SixGe<sub>1-x</sub> epitaxial tunnel layer structure for *P*-channel tunnel fet improvement. *IEEE Trans. Elec. Dev.* 60, 4098 (2013).

- T. Krishnamohan, D. K. S. Raghunathan, and K. C. Saraswat, Double gate strained-Ge heterostructure tunneling fet (TFET) with record high drive currents and <60 mV/dec subthreshold slope. *IEDM Tech. Dig.* 947 (2008).

- S. B. Rahi and B. Ghosh, High-κ double gate junctionless tunnel fet with tunable bandgap. RSC Adv. 5, 54544 (2015).

- S. B. Rahi, P. Asthana, and S. Gupta, Heterogate junctionless tunnel field-effect transistor: Future of low-power devices. *J. Comp. Elec.* 16, 30 (2017).

- J. A. Martino, P. G. D. Agopian, E. Simoen, and C. Claeys, Field effect transistors from mosfet to tunnel-fet analog performance perspective, 12th IEEE International Conference on Solid-State and Integrated Circuit Technology, Guilin, China, October (2014).

- K. Boucart and A. Ionescu, Double gate tunnel fet with high-κ gate dielectric. *IEEE Trans. Elec. Dev.* 54, 1725 (2007).

- S. M. Sze, Physics of Semiconductor Devices, 2nd edn., John Wiley & Sons, Inc., New York (1981).

- P. Chaturvedi and N. Goyal, Effect of gate dielectric thickness on gate leakage in tunnel field Effect transistor, 8th International Caribbean Conference on Devices, Circuits and Systems (ICCDCS), Playa del Carmen, Mexico, March (2012).

- R. Vishnoi and M. J. Kumar, A pseudo 2D-analytical model of dual material gate all-around nanowire tunneling fet. *IEEE Trans. on Elec. Dev.* 61, 2264 (2014).

- Atlas User's Manual device simulation SOFTWARE Silvaco, Inc. 4701 Patrick Henry Drive, Bldg., August (2016).

- R. Asra, M. Shrivastava, Kota V. R. M. Murali, and Rajan K. Pandey, A tunnel FET for V<sub>DD</sub> scaling below 0.6 V with a CMOS-comparable performance. *IEEE Trans. on Elec. Dev.* (2011).

- S. B. Rahi, B. Ghosh, and B. Bishnoi, Temperature effect on hetero structure junctionless tunnel FET. *IOP Science J. of SC* 36, 34002 (2015).

- C. D. Lorente, Innovative tunnel FET architectures, *Joint Interna*tional EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Granada, Spain, March (2018).

- Y. Dong, L. Zhang, X. Li, X. Lin, and M. Chan, A compact model for double-gate heterojunction tunnel FETs. *IEEE Trans. Elec. Dev.* 99 (2016).

- 15. Pranav Kumar Asthana, Bahniman Ghosh, S. B. Rahi, and Yogesh Goswami, Optimal design of high performance H-JLTFET using HfO<sub>2</sub> as gate dielectric for ultra low power applications. *RSC Adv.* 4, 22803 (2014).

- 16. P. K. R. Asthana, Y. Goswami, S. Basak, S. B. Rahi, and B. Ghosh, Improved performance of junctionless tunnel field effect transistor with Si and SiGe hetero-structure for ultra low power applications. *RSC Adv.* 5, 48779 (2015).

- 17. G. Kaur, G. Singh, and M. T. Kaur, Double gate heterostructure based tunnel FET with 51.5 mV/decade subthreshold slope. *IOSR Jour. of VLSI and Sig. Processing (IOSR-JVSP)* 6, 53 (2016).

- A. M. Jossy and T. Vigneswaran, A perspective review of tunnel field effect transistor with steeper switching behavior and low off current (*I*<sub>OFF</sub>) for ultra low power applications. *Int. Jour. Eng. Tech.* (*IJET*) 6, 2092 (2014).

- N. P. Maity, R. Maity, and S. Baishya, Influence of image force effect on tunneling current density for high-κ material ZrO<sub>2</sub> ultra thin films based MOS devices. *Jour. Nanoelec. Optoelec.* 12, 67 (2017).

- 20. N. P. Maity, R. Maity, R. K. Thapa, and S. Baishya, Study of interface charge densities for ZrO<sub>2</sub> and HfO<sub>2</sub> based metal-oxidesemiconductor devices. *Adv.s Mat. Sci. Eng.* 2014, 6 (2014).

- N. P. Maity, R. Maity, and S. Baishya, A tunneling current model with a realistic barrier for uultra-thin high-κ dielectric ZrO<sub>2</sub> material based MOS devices. *Silicon* 10, 1645 (2018).

- 22. N. P Maity, R. Maity, and S. Baishya, Voltage and oxide thickness dependent tunneling current density and tunnel resistivity

model: Application to high-κ material HfO<sub>2</sub> based MOS devices. *Superlattices and Microstr.* 111, 628 (**2017**).

- 23. N. P. Maity, R. Maity, R. K. Thapa, and S. Baishya, A tunneling current density model for ultra thin HfO<sub>2</sub> high-κ dielectric material based MOS devices. *Superlattices and Microstr.* 95, 24 (2016).

- 24. A. Biswas and Adrian M. Ionescu, A capacitance-voltage model for DG-TFET, *Conference: IEEE Silcon Nanoelectronic Workshop* Kyoto, Japan, June (2015).